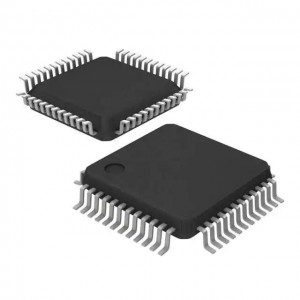

EP1C6Q240C8N IC FPGA 185 I/O 240QFP

Produktparameter

Beschreibung

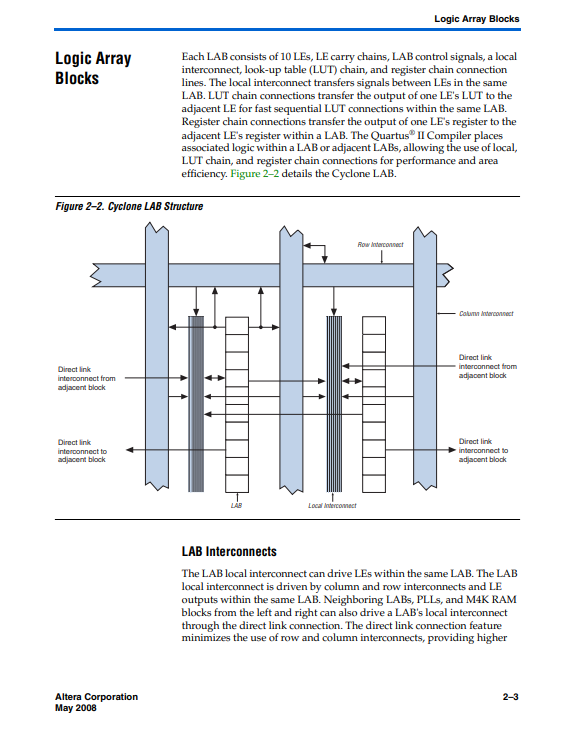

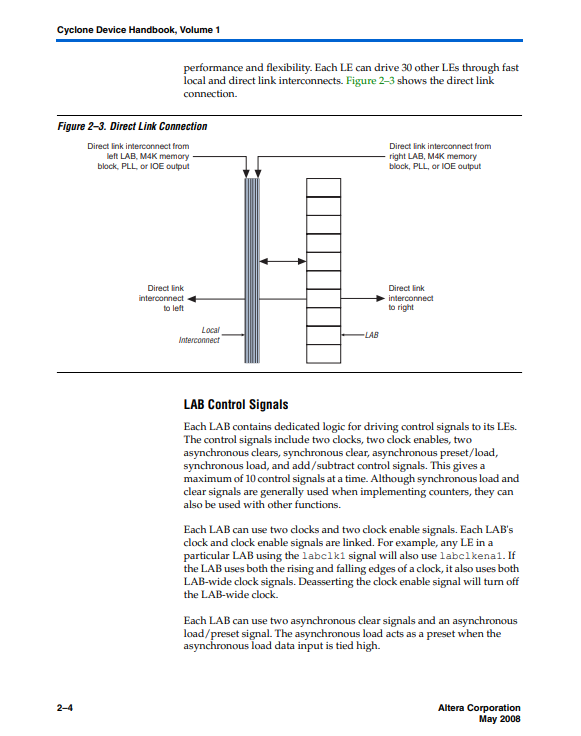

Cyclone®-Geräte enthalten eine zweidimensionale zeilen- und spaltenbasierte Architektur zur Implementierung benutzerdefinierter Logik.Spalten- und Zeilenverbindungen mit unterschiedlichen Geschwindigkeiten stellen Signalverbindungen zwischen LABs und eingebetteten Speicherblöcken bereit.Das Logikarray besteht aus LABs mit 10 LEs in jedem LAB.Ein LE ist eine kleine Logikeinheit, die eine effiziente Implementierung von Benutzerlogikfunktionen bereitstellt.LABs sind auf dem Gerät in Zeilen und Spalten gruppiert.Cyclone-Geräte liegen zwischen 2.910 und 20.060 LEs.M4K-RAM-Blöcke sind echte Dual-Port-Speicherblöcke mit 4K-Bit Speicher plus Parität (4.608 Bit).Diese Blöcke bieten dedizierten echten Dual-Port-, einfachen Dual-Port- oder Single-Port-Speicher mit bis zu 36 Bit Breite bei bis zu 250 MHz.Diese Blöcke sind zwischen bestimmten LABs in Spalten über das Gerät gruppiert.Cyclone-Geräte bieten zwischen 60 und 288 Kbit eingebetteten RAM.Jeder I/O-Pin des Cyclone-Geräts wird von einem I/O-Element (IOE) gespeist, das sich an den Enden von LAB-Reihen und -Spalten um die Peripherie des Geräts herum befindet.I/O-Pins unterstützen verschiedene Single-Ended- und Differential-I/O-Standards, wie den 66- und 33-MHz-, 64- und 32-Bit-PCI-Standard und den LVDS-I/O-Standard mit bis zu 640 Mbit/s.Jedes IOE enthält einen bidirektionalen E/A-Puffer und drei Register zum Registrieren von Eingangs-, Ausgangs- und Ausgangsfreigabesignalen.Doppelfunktionale DQS-, DQ- und DM-Pins zusammen mit Verzögerungsketten (zur Phasenausrichtung von DDR-Signalen) bieten Schnittstellenunterstützung mit externen Speichergeräten wie DDR SDRAM und FCRAM-Geräten mit bis zu 133 MHz (266 Mbps).Cyclone-Geräte bieten ein globales Uhrennetzwerk und bis zu zwei PLLs.Das globale Taktnetzwerk besteht aus acht globalen Taktleitungen, die durch das gesamte Gerät treiben.Das globale Taktnetzwerk kann Takte für alle Ressourcen innerhalb des Geräts bereitstellen, wie z. B. IOEs, LEs und Speicherblöcke.Die globalen Taktleitungen können auch für Steuersignale verwendet werden.Cyclone PLLs bieten Allzweck-Taktung mit Taktvervielfachung und Phasenverschiebung sowie externe Ausgänge für Hochgeschwindigkeits-Differential-I/O-Unterstützung.

| Spezifikationen: | |

| Attribut | Wert |

| Kategorie | Integrierte Schaltungen (ICs) |

| Eingebettet - FPGAs (Field Programmable Gate Array) | |

| Herst | Intel |

| Serie | Cyclone® |

| Paket | Tablett |

| Teilestatus | Veraltet |

| Anzahl der LABs/CLBs | 598 |

| Anzahl der Logikelemente/Zellen | 5980 |

| Gesamte RAM-Bits | 92160 |

| Anzahl der E/A | 185 |

| Spannungsversorgung | 1,425 V ~ 1,575 V |

| Befestigungsart | Oberflächenmontage |

| Betriebstemperatur | 0 °C ~ 85 °C (TJ) |

| Paket / Koffer | 240-BFQFP |

| Gerätepaket des Lieferanten | 240-PQFP (32 x 32) |

| Basisproduktnummer | EP1C6 |

VerwandtPRODUKTE

-

Tel

-

Email

-

skypen

-

WhatsApp

WhatsApp